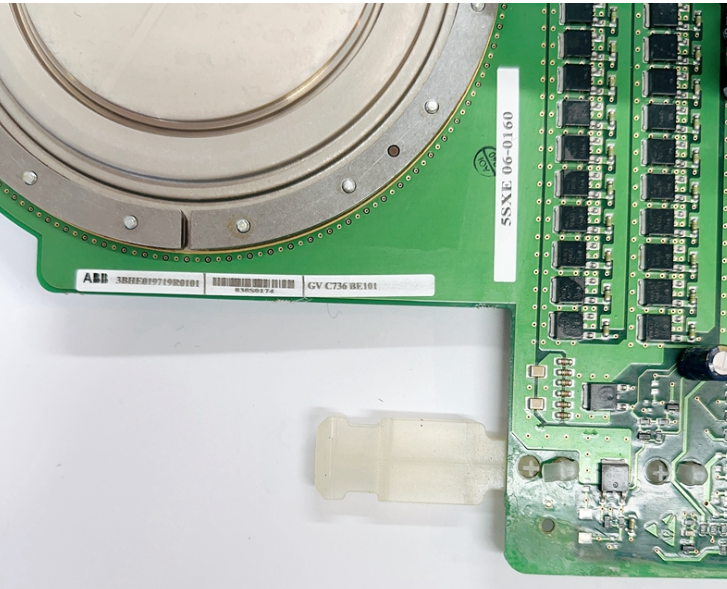

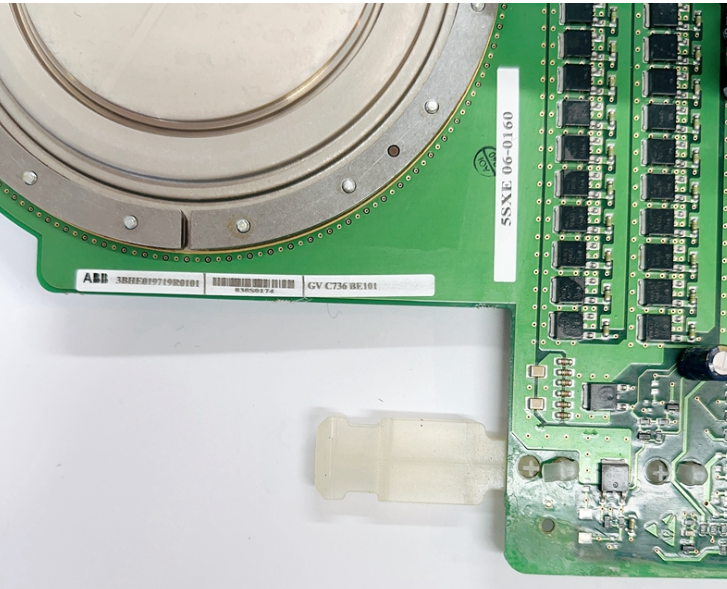

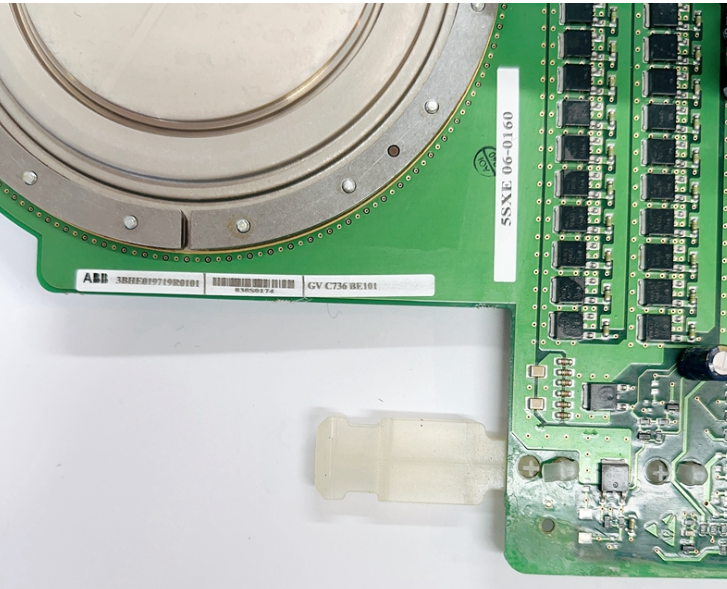

ABB 5SHX1960L0006 3BHB016120R0002 可控硅

ABB 5SHX1960L0006 3BHB016120R0002 可控硅

ABB 5SHX1960L0006 3BHB016120R0002 可控硅

超长指令字( VLIW ) 是指旨在利用指令级并行性(ILP) 的指令集架构。传统的中央处理器(CPU、处理器)大多只允许程序指定指令按顺序执行,而 VLIW 处理器允许程序明确指定指令并行执行。这种设计旨在允许更高的性能,而没有一些其他设计固有的复杂性。

提高处理器性能的传统方法包括将指令分成子步骤,以便部分指令可以同时执行(称为流水线),分派单个指令在处理器的不同部分独立执行(超标量架构),甚至以不同于程序的顺序执行指令(乱序执行)。[1]这些方法都使硬件变得复杂(更大的电路、更高的成本和能源使用),因为处理器必须在内部做出所有决定才能使这些方法起作用。相比之下,VLIW 方法依赖于提供有关同时执行哪些指令以及如何解决冲突的所有决策的程序。实际上,这意味着编译器(用于创建最终程序的软件)变得更加复杂,但硬件比许多其他并行方式要简单。

一个接一个地执行每条指令的处理器(即,非流水线标量架构)可能会低效地使用处理器资源,从而产生潜在的不良性能。通过同时执行顺序指令的不同子步骤(称为流水线),或者甚至像在超标量架构中一样完全同时执行多条指令,可以提高性能。通过以不同于它们在程序中出现的顺序执行指令,称为乱序执行,可以实现进一步的改进。[1]

这三种方法都增加了硬件复杂度。在并行执行任何操作之前,处理器必须验证指令没有相互依赖性。例如,如果第一条指令的结果用作第二条指令的输入,则它们不能同时执行,第二条指令不能在第一条指令之前执行。现代乱序处理器增加了用于调度指令和确定相互依赖性的硬件资源。

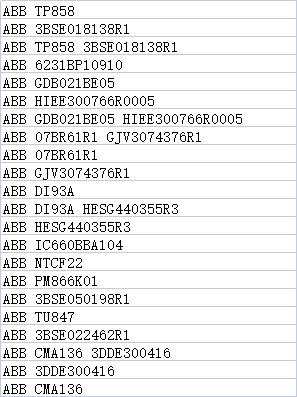

ABB TP858

ABB 3BSE018138R1

ABB TP858 3BSE018138R1

ABB 6231BP10910

ABB GDB021BE05

ABB HIEE300766R0005

ABB GDB021BE05 HIEE300766R0005

ABB 07BR61R1 GJV3074376R1

ABB 07BR61R1

ABB GJV3074376R1

ABB DI93A

ABB DI93A HESG440355R3

ABB HESG440355R3

ABB IC660BBA104

ABB NTCF22

ABB PM866K01

ABB 3BSE050198R1

ABB TU847

ABB 3BSE022462R1

ABB CMA136 3DDE300416

ABB 3DDE300416

ABB CMA136

18030183032