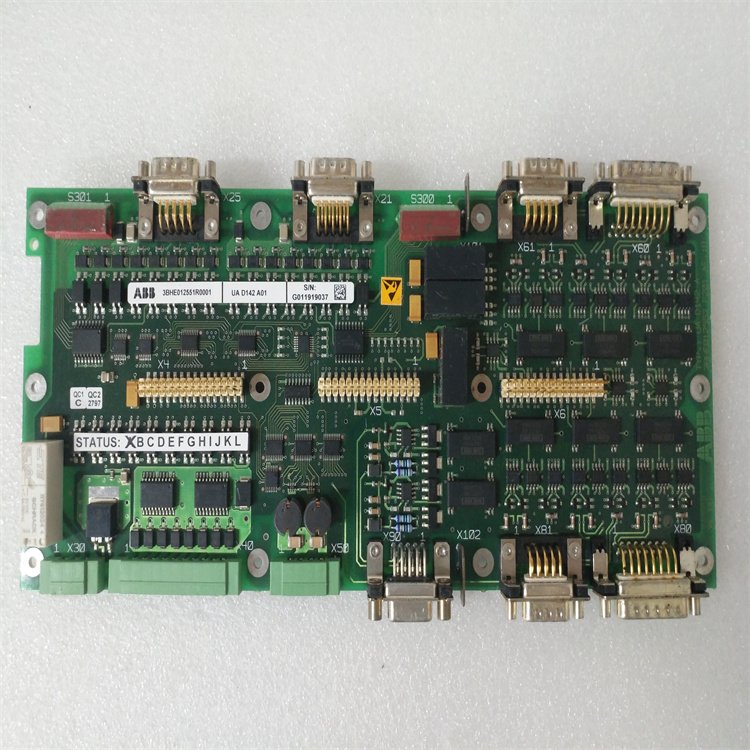

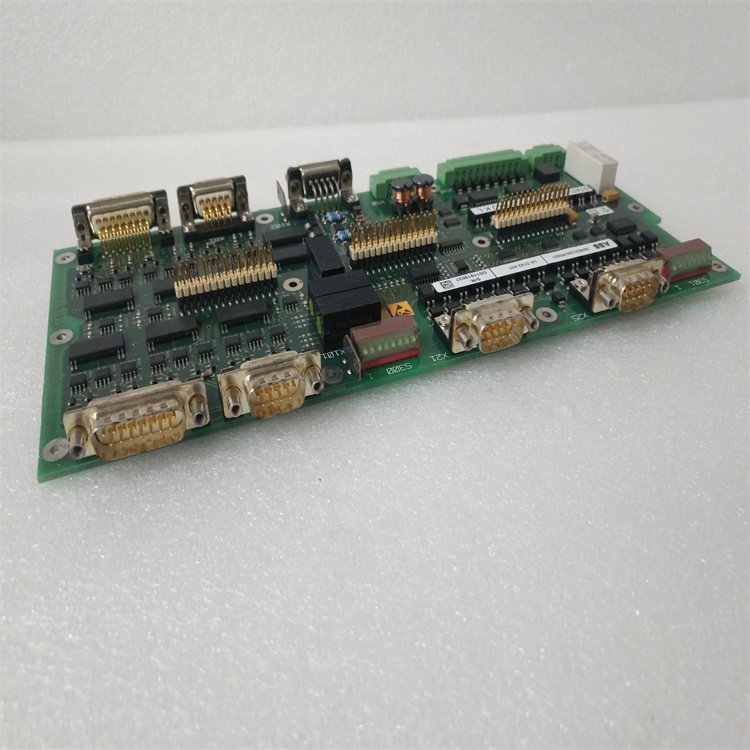

FET3251C0P184C0H2 ABB 输入输出模块

系统的软件设计根据硬件结构的总体划分,也可以分为两大部分来描述。整个系统的运行如图2所示,FPGA和DSP各自的程序独立运行,通过中断信号完成数据的实时交互。FPGA向DSP方向的指令是通过FPGA发送一个EDMA请求,DSP通过响应EDMA请求,建立EDMA通道,开始从FIFO中进行预处理后数据的读取,DSP向FPGA传输数据时,通过向FPGA发送一个中断信号,让其从FIFO中把压缩后的图像数据读出来。

整个系统工作流程可以简单描述如下:系统上电后,首先DSP由flash实现自举,并运行引导程序,之后转入EDMA等待状态,FPGA初始化后等待外部图像采集命令,收到图像采集命令后开始进行图像采集,并对采集到的图像进行预处理,预处理后的图像经过FIFO缓冲,在存储一定量的数据之后,FPGA通过半满信号向DSP发送EDMA请求,等待DSP响应,DSP一旦收到来自FPGA的EDMA请求,立即建立EDMA通道,从FIFO中读取数据到L2存储器,存满一帧图像后DSP开始图像压缩,等待一幅图像压缩完成之后,DSP会向FPGA发送中断信号,FPGA在收到中断信号后开始从 FIFO中读取压缩后的图像数据。一帧数据读完后,判断编码信号是否有效,如果有效则按同样的规则对下一帧图像进行压缩,如果无效则通知DSP结束。

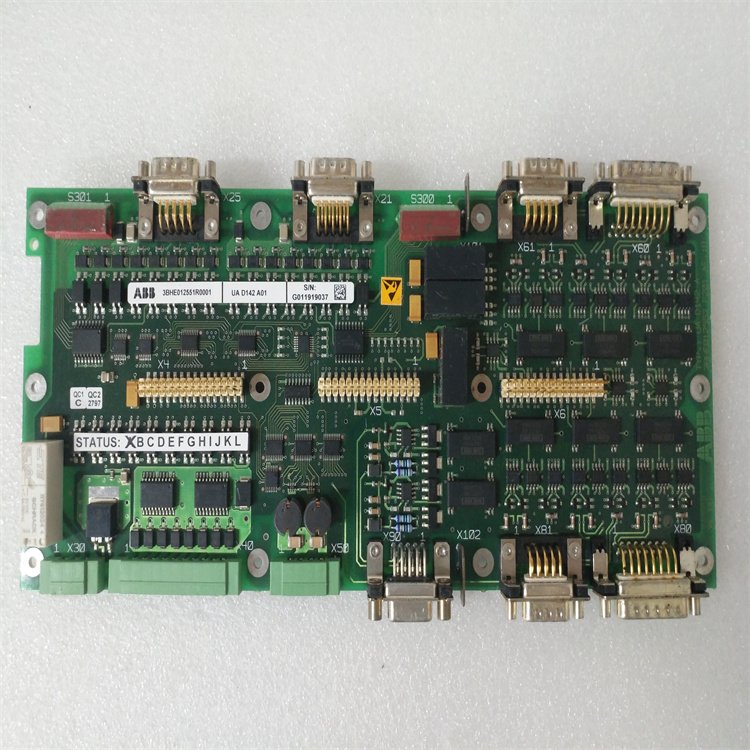

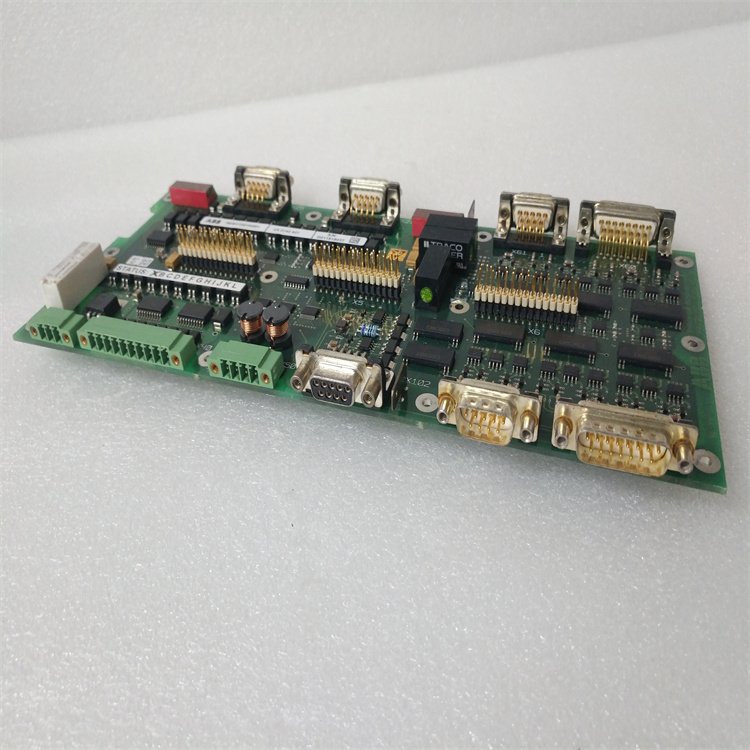

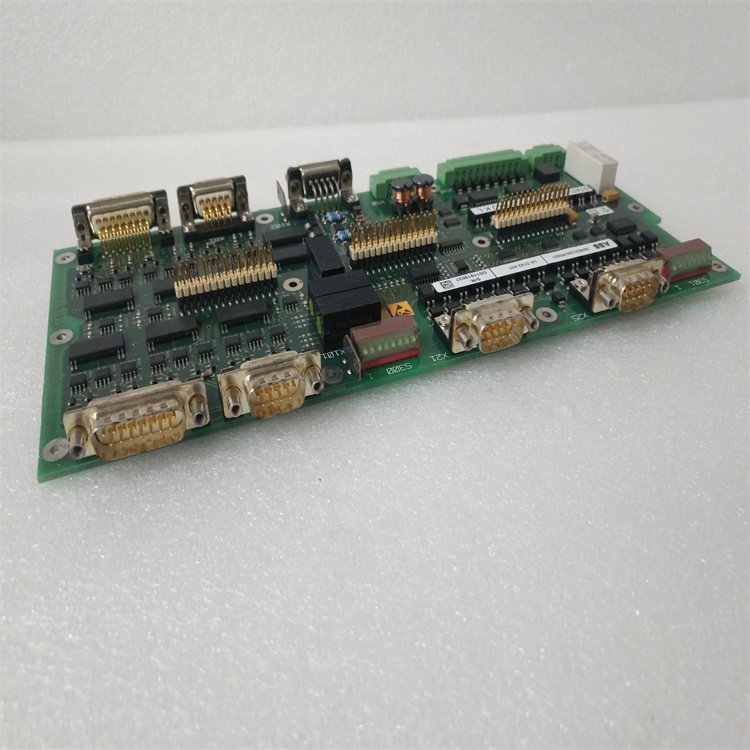

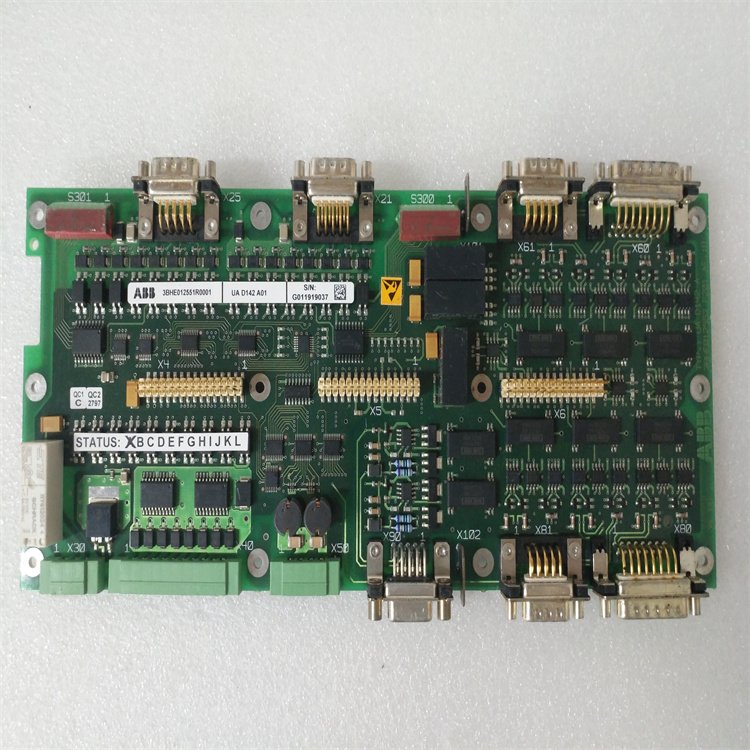

3BHB013085R0001

3BHE009681

5SHX08F4502

CP405 A0 1SAP500405R0001

PM866-2 3BSE050201R1

DI04

CAI04

PM866-23BSE050201R1

PU515A 3BSE032401R1

ICSE08B5 FPR3346501R1012

R474A11XE

REF615A_E

PM864AK01 3BSE018161R1

PCD232A 3BHE022293R01

REF542PLUS 1VCF752000

PPD113B03-26-100100

3BHE023584R2625

PP865A 3BSE042236R2

3ASC25H216A DATX132

3ASC25H208 DATX100

3ASC25H214 DATX130

3ASC25H204 DAPU100

3ASC25H219B DATX133

PPD512A10-150000

LWN2660-6

REF615E E

UNITR0L 1020 UNS0119A-Z,V1

3BHE030579R0003

C1570 3BSE001440R1

PP865A 3BSE042236R2

1MRK00008-KB

SPHSS03

UAD155A0111 3BHE029110R0111

PU515A 3BSE032401R1

PM510V16 3BSE008358R1

CS5133BSE000435R1

SC510 3BSE003832R1

PFSA1403BSE006503R1

x008R21SBP260109R1001

3BHL000986P0006

5SDF0860H0003

5SDF1045H0002

5SHY3545L0010

3BHB013088R0001

3BHE009681R0101

GFD563A101 3BHE046836R0101

SC540 3BSE006096R1

Sc510 3BSE003832R1

5SHY3545L0016

3BHB020720R0002

3BHE019719R0101

uNITR0L1000 7.v3

3BHE014557R0003

18030183032