Field Programmable Gate Array(简称,FPGA)于1985年由XILINX创始人之一Ross Freeman发明,第一颗FPGA芯片XC2064为XILINX所发明,FPGA一经发明,后续的发展速度之快,超出大多数人的想象,近些年的FPGA,始终引领先进的工艺。在通信等领域FPGA有着广泛的应用,通信领域需要高速的通信协议处理方式,另一方面通信协议随时都在修改,不适合做成专门的芯片,所以能够灵活改变的功能的FPGA就成了首选。 并行和可编程是FPGA最大的优势。

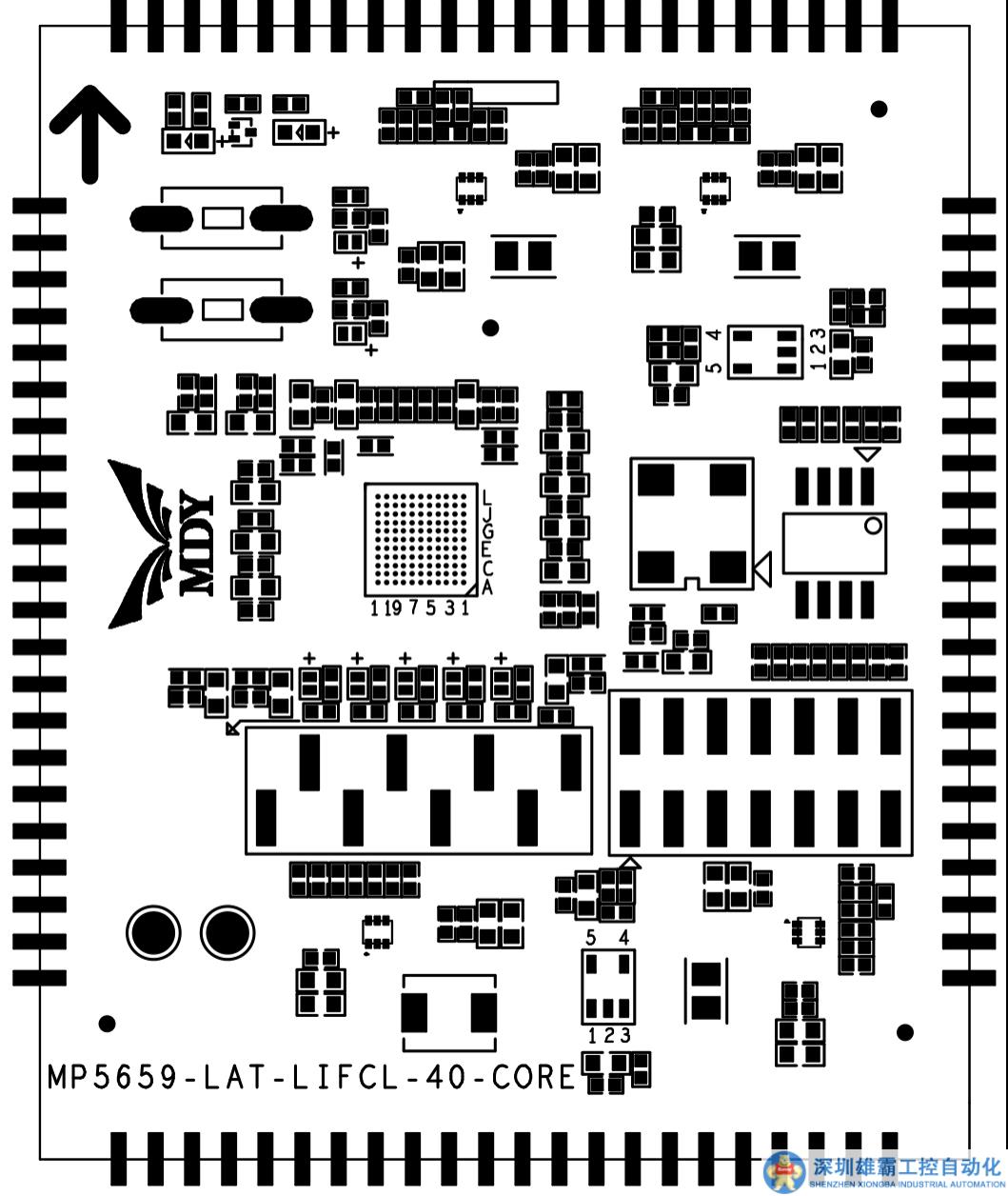

今天分享的核心板采用LATTICE公司CrossLink-NX系列的LIFCL-17-7MG121C作为主控制器,特别适合MIPI总线的开发。核心板采用88个槽形孔与母板连接,其中GPIO信号54个,D-PHY信号20个,电源和地14个。这款核心板能够方便用户对核心板的二次开发利用。核心板结构尺寸为66(mm)× 54(mm)。整个开发系统的结构如图1所示,核心板布局布线图如图2所示。

图1 核心板结构图

图2核心板布局布线图

2.1主要电路设计

2.1.1 FPGA芯片选择

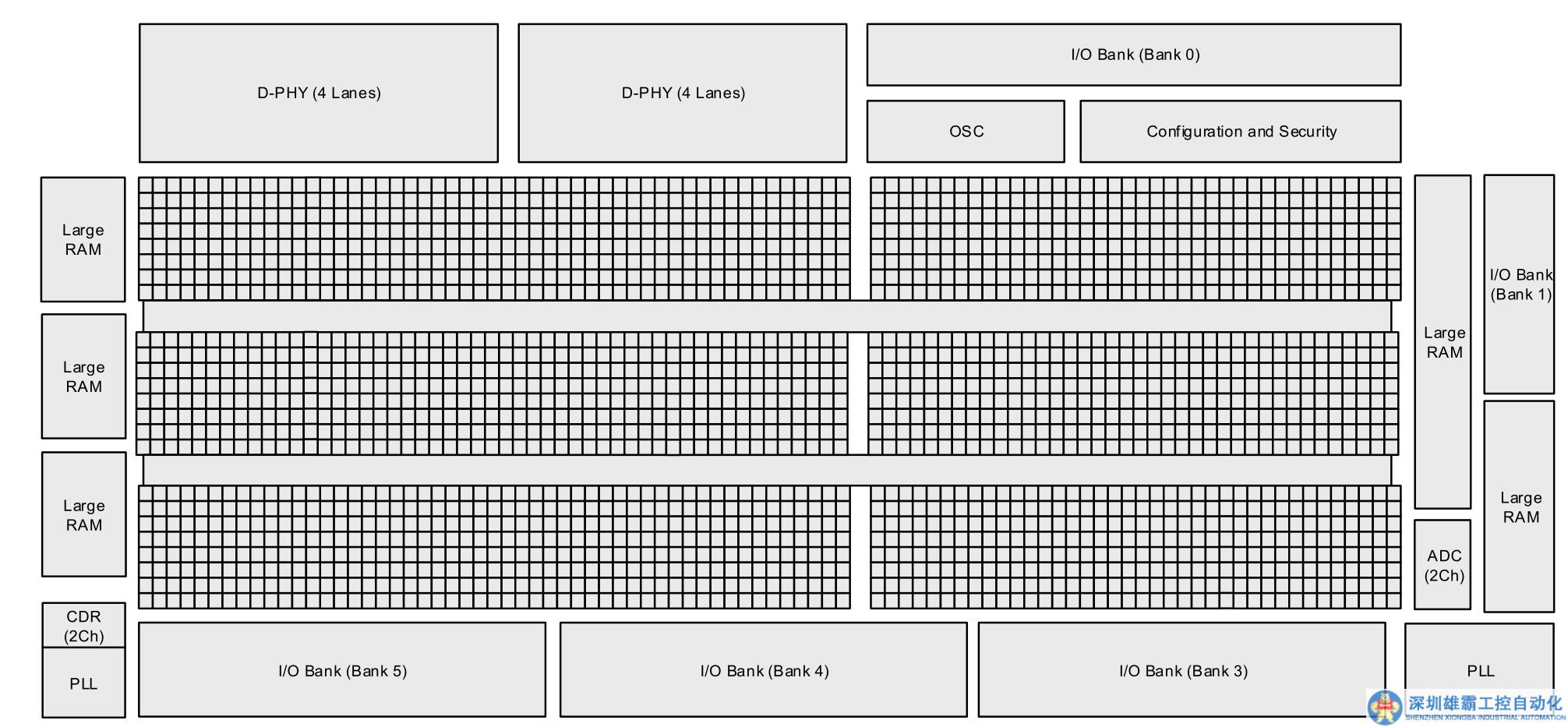

核心板使用的是LATTICE公司CrossLink-NX系列的FPGA芯片,芯片型号LIFCL-17-7MG121C。速度等级为7,温度等级为工业级。此型号为BGA封装,121个引脚,引脚间距为0.5mm。LIFCL-17-7MG121C FPGA的BANK分布如图3所示,FPGA参数如表1所示。

图3 LIFCL-17-7MG121C FPGA BANK分布

表1 FPGA参数表:

| 名称 | 详细参数 |

| 管脚(I/O) | 121 |

| Logic Cells | 17K |

| Embedded Memory (EBR) Blocks (18 Kb) | 24 |

| Embedded Memory (EBR) Bits (Kb) | 432 |

| Distributed RAM Bits (Kb) | 80 |

2.1.2 FPGA BANK接口电平选择

核心板上对外的BANK分别为BANK3/4/5,这些BANK的IO均支持1.8V/1.2V两种电平可调。如果需要更换电平,只需要更换对应位置磁珠即可实现调整,核心板BANK电平调节磁珠位置,如下表所示。

表2 BANK电平调节磁珠位号

| FPGA BANK | +1.2V | +1.8V |

| BANK3 | L17 | L18 |

| BANK4 | L13 | L14 |

| BANK5 | L15 | L16 |

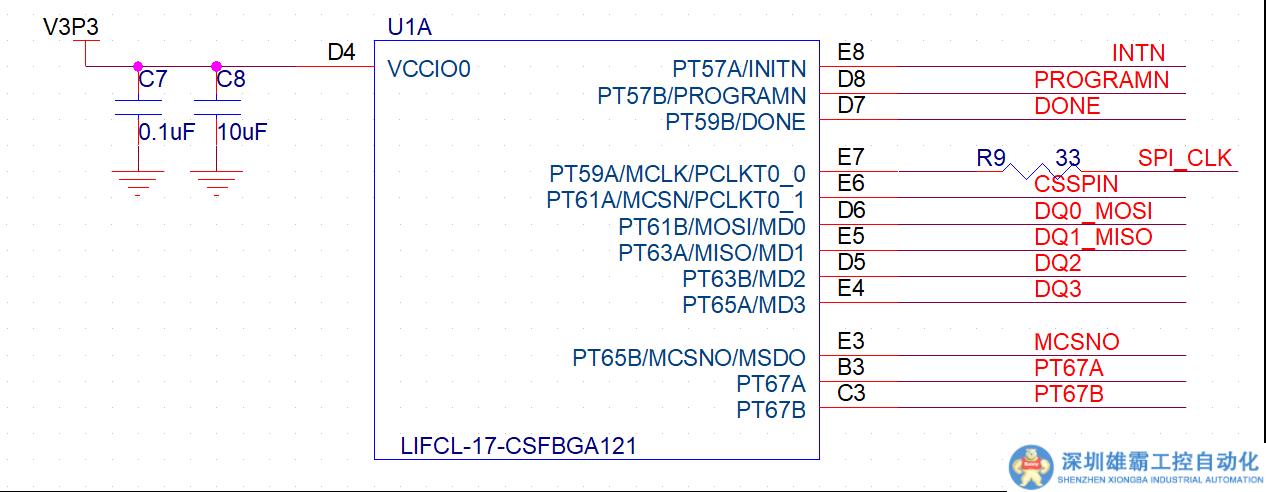

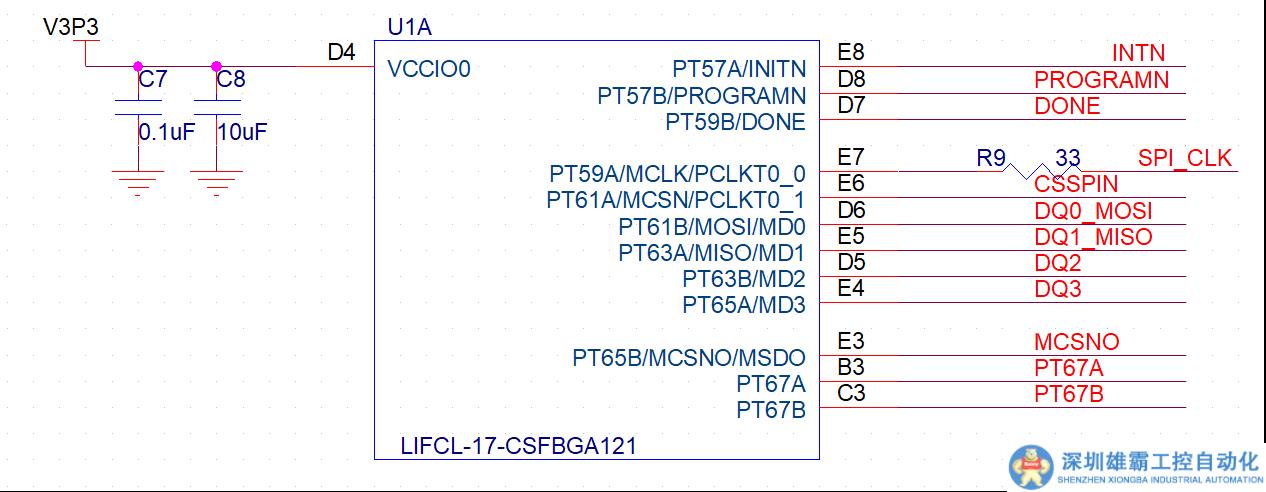

2.1.3 QSPI Flash

核心板配有一片128Mbit大小的Quad-SPI Flash芯片,型号为MX25L12835FM2I,它使用3.3V CMOS电压标准。由于QSPI FLASH的非易失特性,在使用中,它可以存储FPGA的配置Bin文件以及其它的用户数据文件。

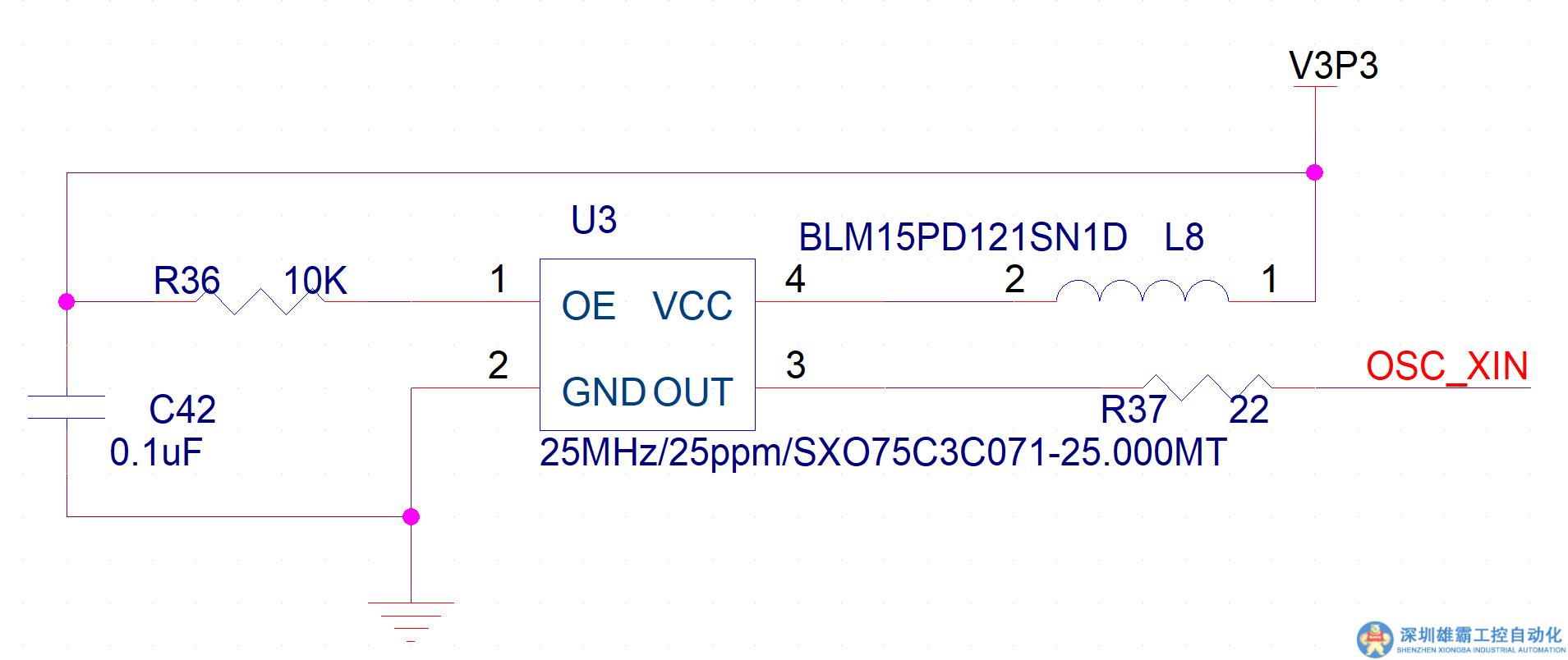

2.1.4 时钟电路

MP5659核心板为了准确适配25MHz的系统晶振。晶振输出连接到FPGA BANK1 的全局时钟,这个全局时钟用来驱动FPGA 内的用户逻辑电路。该时钟源的原理图如图4所示。

图4 时钟电路

2.1.5 JTAG调试口

MP5659核心板板载了一个8PIN的单排贴片JTAG下载调试口,方便用户单独调试FPGA。核心板的JTAG接口连接示意如图5所示。

图5 JTAG调试接口电路图

2.1.5 Flash配置接口

MP5659核心板板载了一个2*7 PIN的双排贴片Flash下载口,方便用户将逻辑烧写到Flash里。核心板的Flash配置接口连接示意如图6所示。

图6 Flash配置接口电路图

2.1.5 核心板电源

核心板集成电源管理,+12V电源输入通过TI 电源芯片TPS563202 产生+1.0V、+1.2V、+1.8V、+3.3V电压,为VCC、VCCIO、晶振、FLASH等供电。+1.8V电压经过ETA5050V0S2F转换为LDO_1.0 V直流,为VCCDPHY、VCCPLLDPHY提供1.0V的电压。+3.3V 电压经过ETA5050V0S2F转换为LDO_1.8V直流,为VCCADPHY、VCCAUX提供1.8V的电压。核心板供电架构如图7所示。

图7 电源拓扑结构图

通过以上描述,我们能够清晰看到这个核心板所含有的接口和功能。这款核心板的槽形孔扩展出了54个IO,其中BANK3、BANK4、BANK5的全部IO的电平可以通过更换核心板上的磁珠来修改,满足用户对+1.2V、+1.8V电平接口的需求;另外核心板也扩展出了8对D-PHY接口。而且IO连接部分,同一个BANK管脚到连接器接口之间走线做了等长和差分处理,对于二次开发来说,非常适合。查看详情

18030183032